Received: 16-01-2025

Revised: 05-02-2025

Accepted: 12-03-2025

## Domino Logic Low Leakage Clock Keeper (LLCKDL) for Effective CMOS Logic Gates

**Dr.M. Chennakesavalu<sup>1</sup>, B.Chandra obulreddy<sup>2</sup>, U. Tanooja<sup>3</sup>, B. Indra senani<sup>4</sup>, S. Prudhvinath Reddy<sup>5</sup>**

<sup>1</sup>Department of ECE

Rajeev Gandhi Memorial College of Engineering & Technology, Nandyal, India, 518501

<sup>2,3,4,5</sup>Department of ECE

Rajeev Gandhi Memorial College of Engineering & Technology, Nandyal, India, 518501

Corresponding author: [chennakesavulu@rgmcet.edu.in](mailto:chennakesavulu@rgmcet.edu.in)

### **Abstract:-**

Propagation delay and power consumption are two critical challenges in deep-submicron CMOS VLSI semiconductor circuits. High leakage currents and increased noise sensitivity further exacerbate these issues, demanding innovative design techniques to enhance efficiency. This study presents a novel approach for designing CMOS logic gates using the Low Leakage Clock Keeper Domino Logic (LLCKDL). The proposed methodology aims to significantly reduce leakage power while improving noise immunity and operational efficiency. The LLCKDL technique incorporates an optimized clock-keeper circuit to minimize unnecessary power dissipation in dynamic logic while maintaining robust signal integrity. To validate its effectiveness, a 16-bit OR gate was designed and simulated using 45 nm CMOS GPDK technology in the Cadence environment. Comparative analysis with existing design methodologies demonstrates substantial improvements. Specifically, LLCKDL achieves an 86.36% reduction in average power consumption, a 56.93% decrease in propagation delay, and an 86.90% improvement in the energy-delay product (EDP). These results highlight the efficiency of LLCKDL in reducing power dissipation while ensuring high-speed operation, making it a promising design paradigm for next-generation low-power CMOS circuits. The proposed approach is particularly beneficial for high-performance VLSI applications, where both power efficiency and speed are crucial. By mitigating leakage power and enhancing noise resilience, LLCKDL offers a viable solution for improving the performance of deep-submicron CMOS logic circuits, paving the way for more energy-efficient and reliable semiconductor devices.

**Keywords:** — Power consumption, Delay, Domino logic, GPDK 45nm CMOS

Received: 16-01-2025

Revised: 05-02-2025

Accepted: 12-03-2025

## 1. Introduction

Because they utilize less power and switch more quickly than static logic circuits, dynamic logic circuits are frequently used in memory design and high-speed signal processing applications. But because of their low threshold voltage, they frequently become troublesome and are negatively impacted by noise interference. The supply voltage is reduced to increase energy efficiency as technology develops. An effective dynamic logic circuit would require a low threshold voltage and subsequent management of leakage and dynamic power consumption [1,2].

The circuit capacitance's charging and discharging processes consume an excessive amount of dynamic power, and the circuit short-circuits to ground, wasting short-circuit power. And practically, whenever a transistor turns off, there will be some leakage power due to the leakage currents. To address these power losses and improve noise immunity, modern circuit designs focus on reducing supply voltage and device sizes. However, if the device dimensions are shrunk, the length of its channel will be reduced and the short-channel effects will also be reduced [3,4].

The research describes LLCKDL, a cutting-edge method for improving CMOS logic gates. This strategy aims to lower leaky power consumption and enhance noise performance. Using Cadence's GPDK 45 nm CMOS technology, an OR gate with 16 inputs has been constructed and simulated at a clock frequency of 10 MHz. The performance results were analysed using power consumption, UNG, and propagation delay. The results show that the proposed design reduces power consumption by at least 74.19%, improves delay by 14.91%, and surpasses the previous designs in terms of energy delay product (EDP) by 67.39%.

In the second subsection of this study, the existing domino logic models were reviewed, and in the third subsection, the suggested CMOS 45 nm logic architecture was described. With this technique, enhanced noise immunity and reduced leakage power are obtained by stacking transistors in an efficient manner to realize high-speed gates with large fan-in" Low propagation latency and power consumption are ensured here by resolving the conflict between the evaluation network and the keeper transistor. This circuit is considerably superior to earlier designs.

The noise immunity of dynamic circuits is negatively impacted by additional supply voltage reduction. Next, technological scaling is allowing the reduction of threshold voltage so that thus enhancing the leakage increases the thinning of gate oxide. The above leakage might improve noise and leakage problems leading to the discharge of the precharge node in domino logic circuits at high frequencies. The presence of multiple parallel paths in the

Received: 16-01-2025

Revised: 05-02-2025

Accepted: 12-03-2025

evaluation logic contributes to higher leakage currents, especially in large fan-in gates, leading to undesirable discharge of the precharge terminal and degraded noise resistance.

To counter this situation, a bigger keeper transistor is advantageous for noise immunity. Higher power dissipation and delay in propagation are drawbacks, though. A larger keeper transistor could lead to conflict between the evaluation logic and the keeper transistor itself by slowing down circuit functioning. At the expense of higher energy consumption, a big keeper transistor will also improve noise immunity and lower leakage current.

Ultimately, the three primary power components that regulate logic circuit power are switching power, short-circuit power, and power leakage. The proposed LLCKDL method effectively addresses these issues by enhancing transistor design, reducing leakage currents, and boosting noise performance, making it a promising strategy for future high-speed digital circuits.

## 2. Existing Techniques in Domino Logic: A critical Review

Domino logic circuits are favoured over other dynamic logic-based digital circuits because of their low power and chip area usage. Large-scale memory systems and fast CPUs are their primary uses. Domino logic utilizes a single PMOS in the pull-up network (PUN), whereas dynamic logic uses many PMOS depending on the number of inputs. One of the primary distinctions is this. This design difference results in higher area and power efficiency for Domino logic circuits.

However, domino logic designs are significantly affected by gate leakage, including subthreshold leakage, which poses a major challenge. Additionally, improper scaling of components can lead to reduced noise immunity in these circuits. Researchers have explored various methods to mitigate leakage power and improve noise resistance in domino logic [11].

In order to improve CMOS domino logic operation, Garg and his colleagues proposed a sharper interference in comparison to low voltage noise contingent domino logic (LVNIDL). The technique was then extended to wide fan-in OR gates and validated using 32nm CMOS HSPICE simulations. For transient analysis, the proposed model operates at a voltage of 0.9 V DC power and a clock frequency of 100 MHz. According to the work's findings, the design is faster and more energy-efficient than any other currently used technique, with a maximum latency improvement of 56.25% and a 76.07% decrease in power savings over CPVT [12].

An ONOFIC pull-down approach was proposed by Magraiya [13] and associates to reduce subthreshold leakage in 32 nm domino circuits based on FinFETs. Both dynamic and inverted pull-down networks incorporate ONOFIC components into their architecture. In comparison to LECTOR-based domino circuits, an OR16 circuit employing this method reduced subthreshold leakage by 48.1% in the low-power (LP) configuration and by 74% in the short-gate (SG) setup, according to HSPICE simulations conducted within a 32 nm BISM4 framework.

Received: 16-01-2025

Revised: 05-02-2025

Accepted: 12-03-2025

Tiwari et al. [14] presented a novel circuit design known as NSCDH, which facilitates the construction of OR gates ranging from 8 to 128 inputs while allowing cascading to subsequent stages. The design integrates an intermediate isolation mechanism that maintains current-free node states, optimizing circuit efficiency. Compared to CDDK, this approach demonstrated a 44.6% reduction in power consumption and a 16.1% improvement in noise immunity for 8-input gates, while achieving a 24.4% reduction in power usage at 128 inputs. HSPICE was utilized to conduct circuit modelling along with conventional 90 nm PTM transistor models.

### 3. Implementation of different Domino Logic

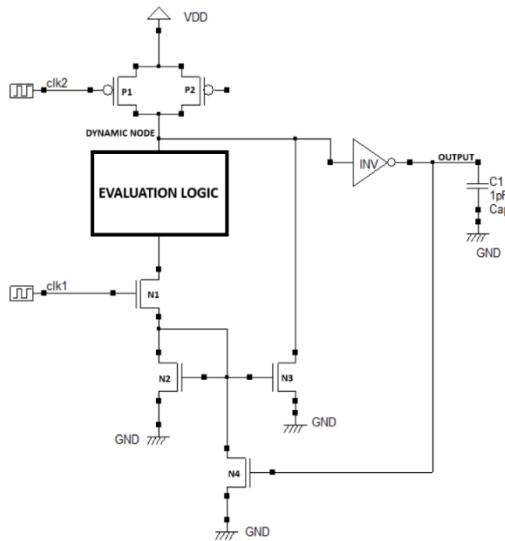

Figure 1 shows the FLDL [15] circuit in its initial implementation. The variation of charge stored in the output capacitance as a result of junction capacitance ( $C_j$ ) [16] is a significant drawback of this design. The keeper, which complements the precharge transistors, is introduced to overcome this difficulty. Further, keeper transistor is one that is driven from the output of the circuit beyond which it acts to enhance circuit stability. In other words, the keeper prevents the unintended release of dynamic nodes through PDN leakage and the related charge-sharing.

Issues Simply stated, the primary limitation of FLDL is the PDN's leaky properties during evaluation, which takes place independent of the magnitude of the applied voltage across all evaluation logic inputs. A considerable contention current flows via the keeper and the PDN when the keeper transistor's size is increased proportionately to the PMOS-PDN current, raising the circuit delay.

Numerically,

$$K_r = W_{kp}/W_{ev}$$

Where  $W_{kp}$  = Transistor Width of the Keeper Circuit

$W_{ev}$  = width of the evaluation logic circuit

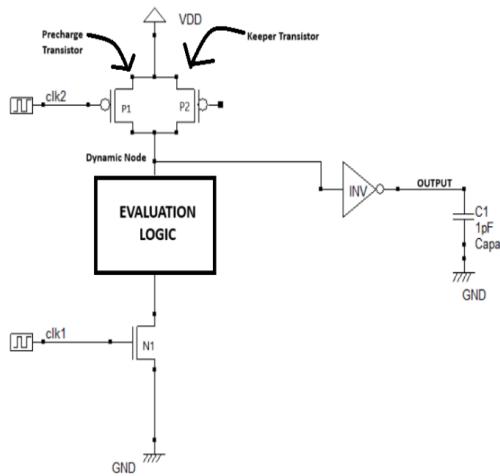

To switch off the power supply during the evaluation phase, an additional transistor (named N1) was placed between the evaluation logic and ground. FDL [19] is the name of the enhanced circuit shown in Figure 2. By increasing delay, the foot transistor (N1) raises the circuit's overall latency. Additionally, as the number of inputs (fan-in) rises, the circuit's noise immunity tends to worsen.

# Power System Technology

ISSN:1000-3673

Received: 16-01-2025

Revised: 05-02-2025

Accepted: 12-03-2025

Fig.1.FLDLCircuitArchitecture [15]

Fig.2.FDLCircuitArchitecture[19]

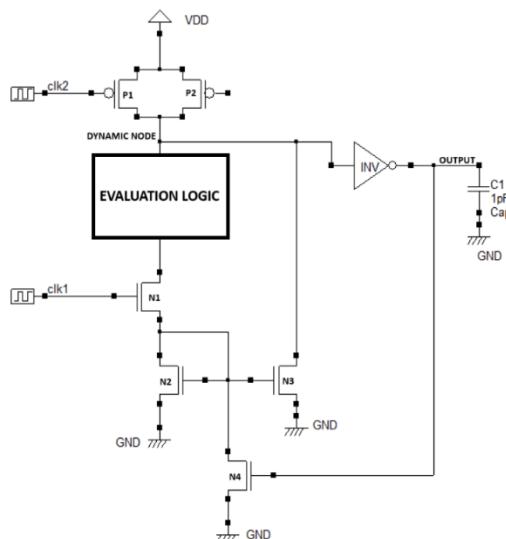

Figure 3 illustrates another domino logic circuit that creates astacking effect by using an extra transistor (N2). Despite improving noise immunity, this modification causes an additional delay in the evaluation process. To lessen this delay, a currentmirror circuit has been constructed using transistors N2 and N3. This technique, which is known as CMFD, boosts speed at the cost of increased size and power consumption due to the additional transistors N2, N3, and N4.

# Power System Technology

ISSN:1000-3673

Received: 16-01-2025

Revised: 05-02-2025

Accepted: 12-03-2025

Fig.3.CMFDL

## Circuit Architecture

Figure 4 illustrates an additional technique that uses an NMOS transistor (M0) in conjunction with AND gates to further improve circuit efficiency. One major drawback of this approach is the addition of a floating gate to transistor M2, which raises power consumption during the precharge phase. This approach is known as (M-HSCD).

Fig.4.M-HSCDCircuitArchitecture[18]

# Power System Technology

ISSN:1000-3673

Received: 16-01-2025

Revised: 05-02-2025

Accepted: 12-03-2025

An alternate domino arrangement is shown in Figure 5, where transistors N2 and N3 are stacked between the ground and the dynamic node. These transistors work together with transistor N1 to enable controlled switching. The floating gate problem in M-HSCD is effectively resolved by this method, called CEDL, which increases power efficiency.

called CEDL, which increases power efficiency.

Fig.5. CEDLCircuitArchitecture [18]

An alternate domino arrangement is shown in Figure 5, where transistors N2 and N3 are stacked between the ground and the dynamic node. These transistors work together with transistor N1 to enable controlled switching.

Fig.6.CSK-DLCircuitArchitecture[18]

Received: 16-01-2025

Revised: 05-02-2025

Accepted: 12-03-2025

#### 4. Novel high performance Domino Logic

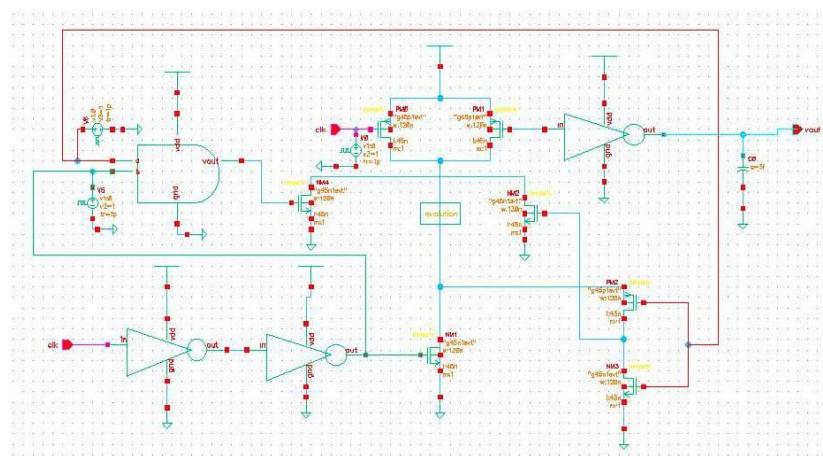

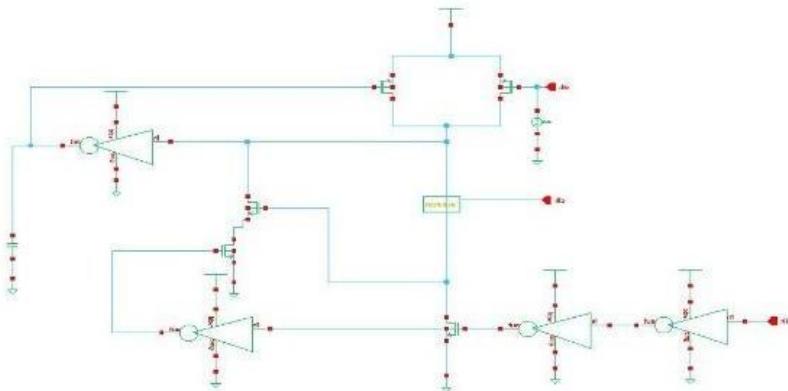

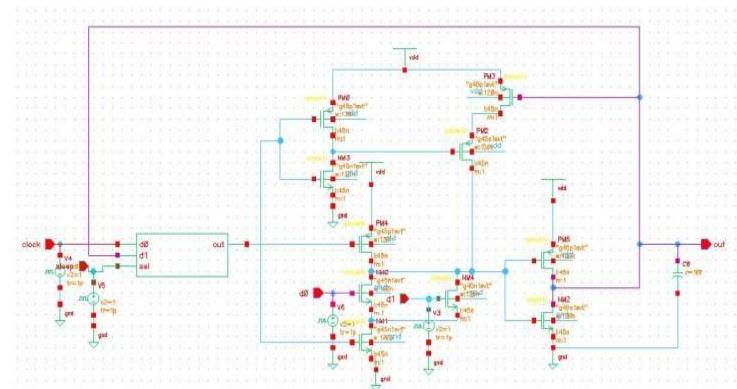

The preceding section dealt with options for actualizing domino logic circuits. Here, we describe a new design that is intended to further improve the capabilities of domino logic. The suggested design, illustrated in Fig 7, is referred to as LLCKDL.

This circuit consists of a footer-equipped NMOS transistor (N1), a clocking PMOS transistor (P1), a pull-down network constructed entirely of NMOS transistors, and a keeper made up of two PMOS transistors (P2 and P3) connected in series. In standby mode, the circuit state is maintained and the clock signal is managed by a MUX. One of the MUX's inputs receives the clock signal, while the other receives the circuit's output

signal.

Fig.7.SuggestedLLCKDL.

When the sleep signal is set to "0" the MUX's output (y) can stay in active operation by following the clock input. When the sleep signal in standby mode is set to "1" the MUX output uses the circuit's output signal (out) as its value. This circuit operates in two modes: Active and Standby.

The sleep signal is turned off but still functional when the clock is in active mode. Transistor P1 is activated to charge the domino node during the precharge phase when the clock signal is "0". Both P3 transistor and keeper are temporarily deactivated during the Eval stage to avoid conflict. If the pull-down network is active, transistor N1 disconnects the dynamic node when the clock signal changes to "1". Transistor P2 stays off if the output is "1" guaranteeing that the keeper stays idle. If the output changes to "0" and the pull-down network stops conducting, the P2 transistor activates. Since the clock remains "1" transistor P3 also activates, maintaining the dynamic node at "1" through the keeper circuit.

**STANDBY:** The output value determines how the circuit behaves in standby mode. When transistor P2's output (out) is set to "1" the keeper stays idle. When transistor N1 activates, the pull-down network conducts and the domino node is dragged to ground, ensuring that the output remains at "1". When transistor P3's output (out) is set to "0" the keeper is deactivated.

Received: 16-01-2025

Revised: 05-02-2025

Accepted: 12-03-2025

Transistor P1 pushes the domino node to a high voltage level in this scenario even when the pull-down network is not conducting, maintaining the output at "0".

The suggested architecture improves upon conventional domino logic by adding an extra PMOS transistor (P3) in the keeper circuit. The reasoning here is that the activation booster keeps the controller inert in the supervision of understanding during the first phase of application, inhibiting content by keeping power requirements within manageable limits. 2 to 1 MUX and 2 input OR gate are designed using this method in this paper.

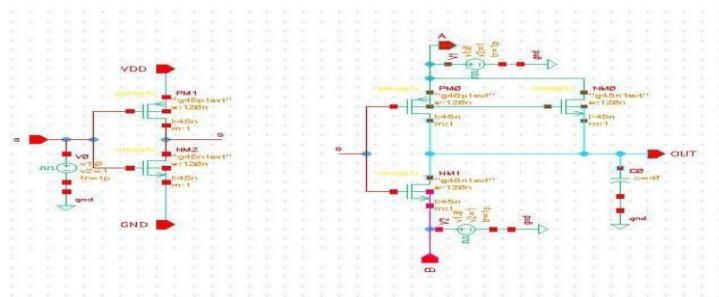

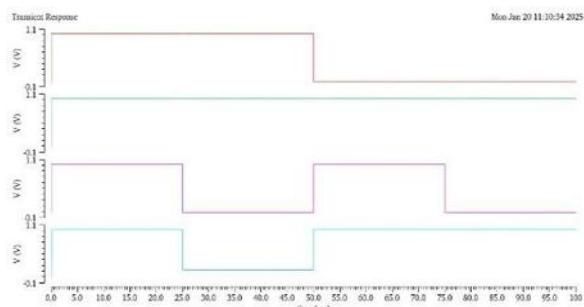

**MUX Design:** Figure 8 depicts a 2-to-1 MUX (MUX) using Gate Diffusion Input (GDI) logic. The PM0 and NM0 transistors make up the MUX. Achieving full-swing output voltage is a frequent problem with GDI-based multipliers. Transistor NM2 is put across PM0 to resolve this problem and preserve complete voltage swing. Fig 9 shows the simulation results for the suggested MUX.

The MUX operates as follows:

Upon receiving a high selection signal (S), input B is sent to output. Upon a low selection signal (S), input A is sent to output.

Fig.8. 2to1MUX

Fig.9. 2to1MUX transient simulation.

# Power System Technology

ISSN:1000-3673

Received: 16-01-2025

Revised: 05-02-2025

Accepted: 12-03-2025

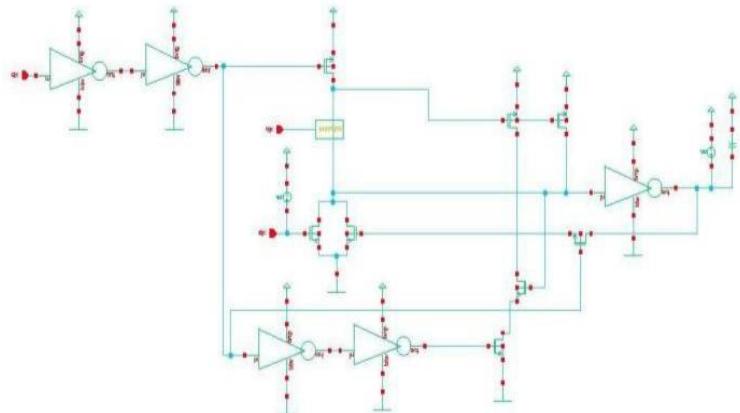

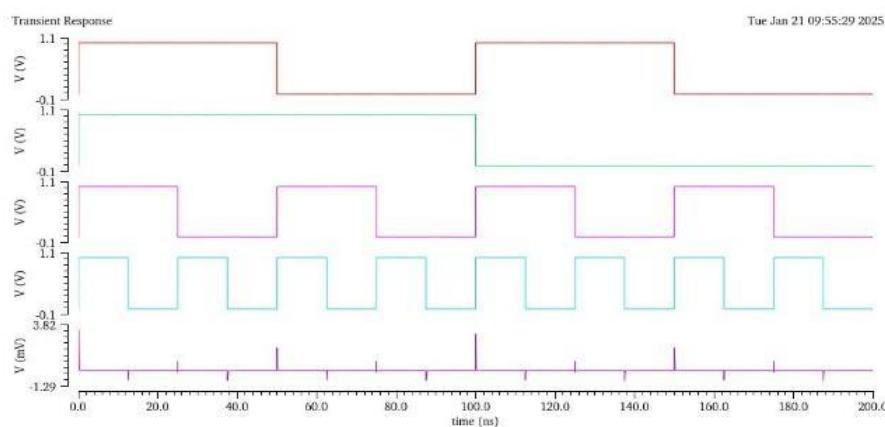

**Input OR gate:** Figure 10 illustrates how the LLCKDL technique is used to create a 2-input OR gate. The N4 and N5 NMOS transistors are reconnected in series by this OR gate for logical evaluation. In the precharge mode, the output voltage stays at its maximum when the sleep signal is set to "0." In active mode, the clock signal is connected to the MUX output (y), and the sleep signal is "0."

The output remains at zero when the sleep signal is in standby mode is set to "1." The OR gate's inputs are denoted by A and B, and the dynamic node voltage is represented by X. When the clock signal is weak, the precharge transistor charges the dynamic node. Consequently, the inverter causes the output voltage to drop and the dynamic node voltage to rise. The values entered now have no effect on the output. The assessment phase starts when the clock signal is high. The dynamic node discharges if one of the inputs (A or B) is high. After a small delay caused by the inverter, this discharge forces the output to transition to high. Figure 11 shows the matching waveforms for the various input conditions of the 2-input OR gate.

Fig.10.A two-input OR gate using the suggested Dominologic

Fig.11.Simulated Waveform of Suggested Two-Input OR Gate

Received: 16-01-2025

Revised: 05-02-2025

Accepted: 12-03-2025

## 5. Implementation and Evaluation of the suggested Domino logic design

Numerous domino logic techniques, such as CEDL, CMFD, CSK-DL, HSCD, FDSTD, and GPKD, are discussed and used in this work along with a recently proposed technique in the CMOS domain. To compare the performance of these designs, simulations are performed using the Cadence Spectre tool considering the 45 nm technology node. Transistor N1's width was increased to four times the minimum channel length ( $L_{min}$ ) in the new design to reduce circuit delay, whereas conventional designs use only twice  $L_{min}$ . Here,  $L_{min}$  is defined as the minimum channel length, which is equal to 45 nanometre. The width of the parallel NMOS transistor was set to double the value of  $L_{min}$  in the evaluation block. Furthermore, the width ratio PMOS to NMOS in inverter was kept constant at 2.5 ( $W_p/W_n$ ), with PMOS and NMOS dimensions set to  $4L_{min}$  and  $2L_{min}$ , respectively. The keeper transistor (P2) was defined as  $4L_{min}$  while the precharge transistor (P1) was set to  $2L_{min}$ .

### Comparison of Various Domino Logic Techniques:

**CMFD (Current Mirror Feedback Domino Logic):** By using the stacking effect, an additional N1 transistor lowers leakage power. N4 is included to minimise noise, and current mirror transistors (N2 & N3) are included to decrease latency.

**CEDL:** connects the dynamic node using a pair of stacked NMOS transistors (N2 & N3), affecting voltage levels according to the sizes of N1 and the evaluation transistors.

**GPKDL:** Implements a grounded PMOS keeper circuit to enhance noise immunity and stability.

**FDSTD (FULLY DEPLETED SUBTHRESHOLD DOMINO LOGIC):** Makes use of NMOS stacking (N2 & N3) to improve power efficiency and lower leakage current. It uses a tiny PMOS keeper to keep the circuit stable and avoid excessive power loss. A PMOS keeper is necessary for each of these circuits in order to guarantee correct domino logic operation. However, a larger PMOS keeper is required as the number of domino logic inputs rises. Higher contention currents between the NMOS pull-down network and the PMOS keeper result from this, which lowers circuit efficiency and raises dynamic power consumption.

**Suggested Approach:** To solve these issues, a new domino logic technique using a delayed keeper circuit with clock gating was developed. In the M-HSCD arrangement with FDL circuits, transistors N2, N3, and P3 are utilized to fix the foot node (N) voltage and minimize current leakage during the evaluation phase. There were two inverters that delayed the clock

Received: 16-01-2025

Revised: 05-02-2025

Accepted: 12-03-2025

signal that controlled transistor N1. NMOS transistors (M0) and an AND gate (G) were integrated to improve evaluation efficiency.

**CSK-DL(Clock-Skewed Keeper Domino Logic):** In the FDL arrangement, the N2, N3, N4, P2, and P3 transistors work together. Transistors N2 and N3 guarantee appropriate dynamic node discharging during the evaluation cycle, while the keeper circuit is shut off prior to the evaluation phase, reducing contention current. Although this design eliminates the conflict between NMOS pull-down networks and PMOS keepers, the additional gates increase the layout area and power dissipation.

**Optimizations in Suggested Design:** Newly suggested domino logic circuitry stacks transistors to reduce leakage energy consumption at the same time as increasing noise immunity. The following important elements would be brought about by the architecture in order to ultimately limit power and delay conflict between the keeper and the evaluation network. During the evaluation phase, PMOS (P3) is introduced to keep the circuit off when it is first switched off. This further minimizes power dissipation and gets rid of contention current. A linked clockgating MUX is part of the updated keeper circuit, which allows for exact clock signal management. The MUX helps maintain circuit state in standby by selecting either the clock or output signal (out).

### Key Metrics for Performance Analysis:

To assess the noise immunity, power efficiency, and robustness of different domino logic circuits, several key performance parameters were considered.

#### Propagation Delay ( $t_p$ ):

This measures the amount of time it takes for a signal to get from the input to the output, evaluated at the circuit's evaluation phase, using the following formula:

$$6. \quad t_p = (t_{pl} + t_{ph})/2$$

The rise and fall time delays are denoted by the letters  $t_{pl}$  and  $t_{ph}$ , respectively.

#### Average Power Consumption ( $P_{avg}$ ):

Determined through transient analysis over 500 ns. A 10 MHz clock frequency and a 1.2 V pulse applied to each input are used for simulations.

#### Product of Power Delay (PDP):

Calculates the overall energy used for switching operations:

$$7. \quad PDP = \text{Average Power} \times \text{Delay}$$

# Power System Technology

ISSN:1000-3673

Received: 16-01-2025

Revised: 05-02-2025

Accepted: 12-03-2025

## EnergyDelayProduct(EDP):

Evaluates the circuit's energy efficiency while carrying out logic operations:

$$8. \quad EDP = PDP \times \text{Propagation Delay}$$

**UnityNoiseGain(UNG):** Determines the circuit's noise immunity by applying a short high-amplitude pulse to both inputs of the evaluation circuit.

TABLE 1: Performance comparison table of existing and proposed techniques to realize 16 input OR gate

| Topology          | Delay (ps) | Average Power Consumed ( $\mu\text{W}$ ) | Power Delay Product (PDP) ( $10^{-18}$ Ws) | Energy Delay Product ( $10^{-18}$ ) ( $\text{EDP J}^2$ ) |

|-------------------|------------|------------------------------------------|--------------------------------------------|----------------------------------------------------------|

| CEDL              | 64.48      | 1.02                                     | 65.7696                                    | 4.24                                                     |

| CMFDL             | 86.24      | 1.42                                     | 119.6208                                   | 10.316                                                   |

| CSK-DL            | 53.37      | 1.76                                     | 93.9312                                    | 5.013                                                    |

| HSCD              | 47.76      | 1.34                                     | 63.9984                                    | 3.056                                                    |

| GPDK              | 43.64      | 0.93                                     | 40.5852                                    | 1.771                                                    |

| LLCKDL (Proposed) | 37.14      | 0.24                                     | 8.9136                                     | 3.31                                                     |

## 6. Conclusion

In order to design a 16-bit OR gate, the novel structure was integrated with contemporary domino logic techniques. There are notable improvements in power efficiency, delay, power-delay product, and energy-delay product as compared to conventional techniques. This realization is well suitable for low-power and high-performance applications.

Performance measures indicated that the suggested design reduces power consumption by 76.47%, 83.10%, 86.36%, 82.09%, and 74.19% compared to CEDL, CMFDL, CSK-DL, HSCD, and GPDK, respectively. The Delay is also minimized by 42.39%, 56.94%, 30.39%, 22.24%, and 14.91% relative to the same techniques. Furthermore, PDP is improved by 86.45%, 92.55%, 90.51%, 86.08%, and 78.03%, while EDP sees enhancements of 78.10%, 83.91%, 85.23%, 79.64%, and 67.39%, respectively.

Future research could explore on-chip training circuits and alternative low-power strategies to further optimize energy efficiency. Further research may improve overall performance by fine-tuning keep topology and optimising transistor aspect ratios in pull-down network.

Received: 16-01-2025

Revised: 05-02-2025

Accepted: 12-03-2025

## REFERENCES

- [1] S.H. Choi, B.C. Paul, K. Roy, Dynamic noise analysis with capacitive and inductive coupling, in: Proceedings of the 7th Asia and South Pacific Design Automation Conference(ASPDAC), 2002. January 11.

- [2] T.K. Gupta, A.K. Pandey, O.P. Meena, Analysis and design of lector-based dual-Vt domino logic with reduced leakage current, *Circuit World* 43 (3) (2017) 97–104, <https://doi.org/10.1108/CW-03-2017-0013>.

- [3] I.C. Wey, C.W. Chang, Y.C. Liao, H.J. Chou, Noise-tolerant dynamic CMOS circuits design by using true single-phase clock latching technique, *Int. J. Circuit Theor. Appl.* 43 (7) (2015) 854–865, <https://doi.org/10.1002/cta.1976>.

- [4] A. Peiravi, M. Asyaei, Robust low leakage controlled keeper by current-comparison domino for wide fan-in gates, *Integration* 45 (1) (2012) 22–32, <https://doi.org/10.1016/j.vlsi.2011.07.002>.

- [5] S.M. Sharroush, Y.S. Abdalla, A.A. Dessouki, Impact of technology scaling on the performance of domino CMOS logic, in: Proceedings of the International Conference on Electronic Design, 2008, pp. 1–3.

- [6] S. Singhal, A. Mehra, U. Tripathi, Power reduction in domino logic using clock gating in 16 nm CMOS technology, in: Proceedings of the 6th International Conference on Signal Processing and Integrated Networks (SPIN) 2019, IEEE Publications, 2019, pp. 274–277.

- [7] Y. Sun, W. He, Z. Mao, V. Kursun, Variable strength keeper for high-speed and lowleakage carbon nanotube domino logic, *Microelectron. J.* 62 (2017) 12–20, <https://doi.org/10.1016/j.mejo.2017.01.010>.

- [8] A.A. Angeline, V.S. Kanchana Bhaaskaran, Design impacts of delay invariant highspeed clock delayed dual keeper domino circuit, *IET Circuits Devices Syst.* 13 (8) (2019) <https://doi.org/10.1049/iet-cds.2018.5410>.

- [9] M.R. Nandini, P. Mor, J. Keller, A comparative study of static and dynamic CMOS logic, *Int. J. Curr. Eng. Technol.* 6 (2016) 1019–1021.

- [10] S. Garg, T.K. Gupta, Low power domino logic circuits in deep submicron technology using cmos, *Eng. Sci. Technol. Int. J.* 21 (4) (2018) 625–638.

- [11] N. Liao, X. Cui, K. Liao, K. Ma, D. Wu, W. Wei, R. Li, D. Yu, Low power adiabatic logic based on finFETs, *Sci. China Inf. Sci.* 57 (2) (2014) 1–13.

- [12] S. Garg, T.K. Gupta, A.K. Pandey, D. Pandey, P. Rajpoot, The effect of noise robustness on domino using silicon nano materials, *Silicon* (2024) 1–15, <https://doi.org/10.1007/s12633-024-02854-8>.

- [13] J. Rajesh, Pandey, A. Kori, S. Magraiyah, V. Gupta, T. Verma, Evaluation of dualONOFIC method for subthreshold leakage Reduction in domino circuit, *Int. J. Electron.* (2023), <https://doi.org/10.1080/00207217.2023.2278439>.

# Power System Technology

## ISSN:1000-3673

Received: 16-01-2025

Revised: 05-02-2025

Accepted: 12-03-2025

- [14] M. Tiwari, V. Chaurasia, Nodal state comparison-based dynamic hold technique for low power OR gates in domino logic, IETE J. Res. (2023) 1–11, 10.1080/03772063.2023.2194263. <https://doi.org/>

- [15] H. Mahmoodi-Meimand, K. Roy, Diode footed domino: a leakage tolerant high fanin dynamic circuit design style, IEEE Trans. Circuits Syst. I 51 (3)(2004)[https://doi.org/10.1109/TCSI.2004.823665. 495–503](https://doi.org/10.1109/TCSI.2004.823665),

- [16] C.H. Cheng, S.C. Chang, J.S. Wang, W.B. Jone, Charge sharing fault detection for CMOS domino logic circuits, in: Proceedings of the International Symposium on Defect and Fault Tolerance in VLSI Systems, 1999, pp. 77–85, <https://doi.org/10.1109/DFTVS.1999.802872>.

- [17] T.K. Gupta, K. Khare, Lector with footed diode inverter: a technique for leakage reduction in domino circuits, Circuits Syst. Signal Process. 32 (6)(2013)2707–2722, <https://doi.org/10.1007/s00034-013-9615-2>.

- [18] S.A. Tawfik, V. Kursun, High-speed finFET domino logic circuits with independent gate-biased double-gate keepers providing dynamically adjusted immunity to noise, in: Proceedings of the of IEEE International Conference 2007, pp. on Microelectronics, 175–178, <https://doi.org/10.1109/ICM.2007.4497687>

- [19] N. Gong, B. Guo, J. Lou, J. Wang, Analysis and optimization of leakage current characteristics in sub-65 Nm Dual V<sub>t</sub> footed domino circuits, Microelectron. J. 39 (9) (2008) 1149–1155, <https://doi.org/10.1016/j.mejo.2008.01.028>.

- [20] F. Moradi, T.V. Vu Cao, E.I. Vatajelu, A. Peiravi, H. Mahmoodi, D.T. Wisland, Domino logic designs for high performance and leakage tolerant applications, Integration 46 (3) (2013) 247–254, <https://doi.org/10.1016/j.vlsi.2012.04.005>